## **Excellent Integrated System Limited**

Stocking Distributor

Click to view price, real time Inventory, Delivery & Lifecycle Information:

Silicon Labs CY2SSTV857ZI-27

For any questions, you can email us directly: <u>sales@integrated-circuit.com</u>

**Distributor of Silicon Labs: Excellent Integrated System Limited** Datasheet of CY2SSTV857ZI-27 - IC CLK BUF DDR 200MHZ 1CIRC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

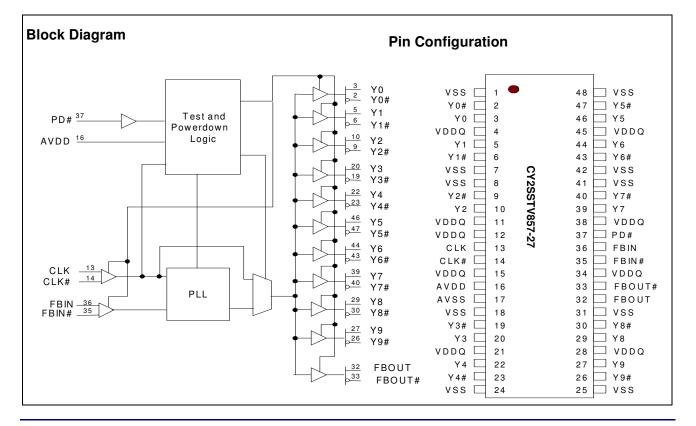

## CY2SSTV857-27

## Differential Clock Buffer/Driver DDR333/PC2700-Compliant

#### Features

- Operating frequency: 60 MHz to 200 MHz

- Supports 266, 333 MHz DDR SDRAM

- 10 differential outputs from 1 differential input

- Spread-Spectrum-compatible

- Low jitter (cycle-to-cycle): < 75

- Very low skew: < 100 ps</li>

- Power management control input

- High-impedance outputs when input clock < 10 MHz

- 2.5V operation

- Pin-compatible with CDC857-2 and -3

- 48-pin TSSOP package

- Industrial temp. of –40° to +85°C

- Conforms to JEDEC DDR specification

#### Description

The CY2SSTV857-27 is a high-performance, low-skew, low-jitter zero-delay buffer designed to distribute differential clocks in high-speed applications. The CY2SSTV857-27 generates ten differential pair clock outputs from one differential pair clock input. In addition, the CY2SSTV857-27 features differential feedback clock outputs and inputs. This allows the CY2SSTV857-27 to be used as a zero-delay buffer.

When used as a zero-delay buffer in nested clock trees, the CY2SSTV857-27 locks onto the input reference and translates with near-zero delay to low-skew outputs.

Rev 1.0, November 21, 2006

2200 Laurelwood Road, Santa Clara, CA 95054

Tel:(408) 855-0555

Fax:(408) 855-0550

www.Spectrum

Page 1 of 8 www.SpectraLinear.com

## CY2SSTV857-27

### Pin Description

| Pin Number                             | Pin Name  | <b>I/O</b> <sup>[1]</sup> | Pin Description                                                                                                                                                                                              | Electrical<br>Characteristics |

|----------------------------------------|-----------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 13, 14                                 | CLK, CLK# | I                         | Differential Clock Input.                                                                                                                                                                                    | LV Differential Input         |

| 35                                     | FBIN#     | I                         | Feedback Clock Input. Connect to FBOUT# for accessing the PLL.                                                                                                                                               | Differential Input            |

| 36                                     | FBIN      | I                         | Feedback Clock Input. Connect to FBOUT for accessing the PLL.                                                                                                                                                |                               |

| 3, 5, 10, 20, 22                       | Y(0:4)    | 0                         | Clock Outputs                                                                                                                                                                                                | Differential Outputs          |

| 2, 6, 9, 19, 23                        | Y#(0:4)   | 0                         | Clock Outputs                                                                                                                                                                                                |                               |

| 27, 29, 39, 44, 46                     | Y(9:5)    | 0                         | Clock Outputs                                                                                                                                                                                                | Differential Outputs          |

| 26, 30, 40, 43, 47                     | Y#(9:5)   | 0                         | Clock Outputs                                                                                                                                                                                                |                               |

| 32                                     | FBOUT     | 0                         | <b>Feedback Clock Output</b> . Connect to FBIN for normal operation. A bypass delay capacitor at this output will control Input Reference/Output Clocks phase relationships.                                 | Differential Outputs          |

| 33                                     | FBOUT#    | 0                         | <b>Feedback Clock Output</b> . Connect to FBIN# for normal operation. A bypass delay capacitor at this output will control Input Reference/Output Clocks phase relationships.                                |                               |

| 37                                     | PD#       | I                         | <b>Power Down# Input</b> . When PD# is set HIGH, all Q and Q# outputs are enabled and switch at the same frequency as CLK. When set LOW, all Q and Q# outputs are disabled Hi-Z and the PLL is powered down. |                               |

| 4, 11,12,15,21,28,<br>34, 38, 45       | VDDQ      |                           | 2.5V Power Supply for Output Clock Buffers.                                                                                                                                                                  | 2.5V Nominal                  |

| 16                                     | AVDD      |                           | <b>2.5V Power Supply for PLL</b> . When VDDA is at GND, PLL is bypassed and CLK is buffered directly to the device outputs. During disable (PD# = 0), the PLL is powered down.                               | 2.5V Nominal                  |

| 1, 7, 8, 18, 24, 25,<br>31, 41, 42, 48 | VSS       |                           | Common Ground                                                                                                                                                                                                | 0.0V Ground                   |

| 17                                     | AVSS      |                           | Analog Ground                                                                                                                                                                                                | 0.0V Analog<br>Ground         |

#### Zero-delay Buffer

When used as a zero-delay buffer the CY2SSTV857-27 will likely be in a nested clock tree application. For these applications the CY2SSTV857-27 offers a differential clock input pair as a PLL reference. The CY2SSTV857-27 then can lock onto the reference and translate with near-zero delay to low-skew outputs. For normal operation, the external feedback input, FBIN, is connected to the feedback output, FBOUT. By connecting the feedback output to the feedback input the propagation delay through the device is eliminated. The PLL works to align the output edge with the input reference edge thus producing a near-zero delay. The reference frequency affects the static phase offset of the PLL and thus the relative delay between the inputs and outputs. When VDDA is strapped LOW, the PLL is turned off and bypassed for test purposes.

#### **Power Management**

Output enable/disable control of the CY2SSTV857-27 allows the user to implement power management schemes into the design. Outputs are three-stated/disabled when PD# is asserted low (see *Table 1*).

Note:

A bypass capacitor (0.1μF) should be placed as close as possible to each positive power pin (<0.2"). If these bypass capacitors are not close to the pins, their high-frequency filtering characteristic will be cancelled by the lead inductance of the traces.</li>

## CY2SSTV857-27

#### Table 1. Function Table

| Inputs |     |          | Outputs  |      |      |       |        |              |

|--------|-----|----------|----------|------|------|-------|--------|--------------|

| AVDD   | PD# | CLK      | CLK#     | Y    | Y#   | FBOUT | FBOUT# | PLL          |

| GND    | Н   | L        | Н        | L    | Н    | L     | Н      | BYPASSED/OFF |

| GND    | Н   | Н        | L        | Н    | L    | Н     | L      | BYPASSED/OFF |

| Х      | L   | L        | Н        | Z    | Z    | Z     | Z      | Off          |

| Х      | L   | Н        | L        | Z    | Z    | Z     | Z      | OFF          |

| 2.5V   | Н   | L        | Н        | L    | Н    | L     | Н      | On           |

| 2.5V   | Н   | Н        | L        | Н    | L    | Н     | L      | On           |

| 2.5V   | Н   | < 10 MHz | < 10 MHz | Hi-Z | Hi-Z | Hi-Z  | HI-Z   | Off          |

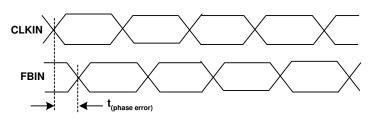

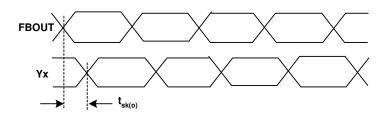

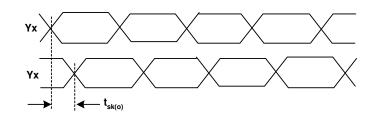

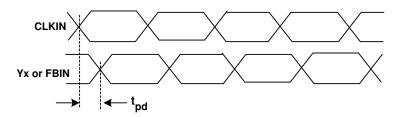

Figure 1. Phase Error and Skew Waveforms

Figure 2. Propagation Delay Time t<sub>PLH</sub>, t<sub>PHL</sub>

**Distributor of Silicon Labs: Excellent Integrated System Limited** Datasheet of CY2SSTV857ZI-27 - IC CLK BUF DDR 200MHZ 1CIRC Contact us: sales@integrated-circuit.com Website: www.integrated-circuit.com

## CY2SSTV857-27

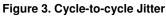

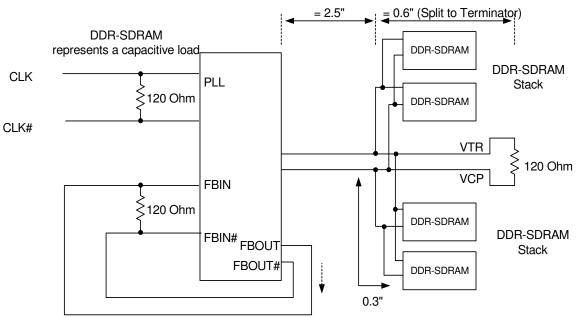

Output load capacitance for 2 DDR-SDRAM Loads: 5 pF< CL< 8 pF

Figure 4. Clock Structure # 1

Output load capacitancce for 4 DDR-SDRAM Loads: 10 pF < CL < 16 pF

Figure 5. Clock Structure # 1

## CY2SSTV857-27

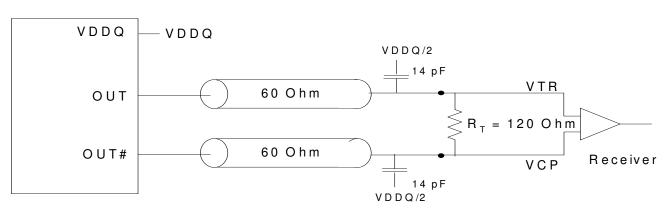

Figure 6. Differential Signal Using Direct Termination Resistor

## CY2SSTV857-27

#### Absolute Maximum Conditions<sup>[2]</sup>

| Input Voltage Relative to V <sub>SS</sub> :                      | V <sub>SS</sub> -0.3V   |

|------------------------------------------------------------------|-------------------------|

| Input Voltage Relative to V <sub>DDQ</sub> or AV <sub>DD</sub> : | V <sub>DDQ</sub> + 0.3V |

| Storage Temperature:                                             | –65 ℃ to + 150 ℃        |

| Operating Temperature:                                           | 0℃ to +85℃              |

| Maximum Power Supply:                                            | 3.5V                    |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, Vin and Vout should be constrained to the range:

$V_{SS} < (V_{in} \text{ or } V_{out}) < V_{DDQ}.$

Unused inputs must always be tied to an appropriate logic voltage level (either V<sub>SS</sub> or V<sub>DDQ</sub>).

| <b>DC Electrical Specifications</b> (AV <sub>DD</sub> = V <sub>DDQ</sub> | $_{\rm Q}$ = 2.5v ± 5%, T <sub>A</sub> = 0 °C to +85 °C) <sup>[3]</sup> |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------|

|--------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Parameter        | Description                                        | Condition                                          | Min.                           | Тур.        | Max.                        | Unit |

|------------------|----------------------------------------------------|----------------------------------------------------|--------------------------------|-------------|-----------------------------|------|

| V <sub>DDQ</sub> | Supply Voltage                                     | Operating                                          | 2.38                           | 2.5         | 2.63                        | V    |

| V <sub>IL</sub>  | Input Low Voltage                                  | PD#                                                |                                |             | $0.3 \times V_{DDQ}$        | V    |

| V <sub>IH</sub>  | Input High Voltage                                 |                                                    | $0.7 \times V_{DDQ}$           |             |                             | V    |

| V <sub>ID</sub>  | Differential Input Voltage <sup>[4]</sup>          | CLK, FBIN                                          | 0.36                           |             | $V_{DDQ} + 0.3$             | V    |

| V <sub>IX</sub>  | Differential Input Crossing Voltage <sup>[5]</sup> | CLK, FBIN                                          | (V <sub>DDQ</sub> /2) –<br>0.2 | $V_{DDQ}/2$ | (V <sub>DDQ</sub> /2) + 0.2 | V    |

| I <sub>IN</sub>  | Input Current [CLK, FBIN, PD#]                     | $V_{IN} = 0V \text{ or } V_{IN} = V_{DDQ}$         | -10                            |             | 10                          | μA   |

| I <sub>OL</sub>  | Output Low Current                                 | V <sub>DDQ</sub> = 2.375V, V <sub>OUT</sub> = 1.2V | 26                             | 35          |                             | mA   |

| I <sub>OH</sub>  | Output High Current                                | $V_{DDQ} = 2.375V, V_{OUT} = 1V$                   | -28                            | -32         |                             | mA   |

| V <sub>OL</sub>  | Output Low Voltage                                 | V <sub>DDQ</sub> = 2.375V, I <sub>OL</sub> = 12 mA |                                |             | 0.6                         | V    |

| V <sub>OH</sub>  | Output High Voltage                                | $V_{DDQ} = 2.375V, I_{OH} = -12 \text{ mA}$        | 1.7                            |             |                             | V    |

| V <sub>OUT</sub> | Output Voltage Swing <sup>[6]</sup>                |                                                    | 1.1                            |             | $V_{DDQ} - 0.4$             | V    |

| V <sub>OC</sub>  | Output Crossing Voltage <sup>[7]</sup>             |                                                    | (V <sub>DDQ</sub> /2) –<br>0.2 | $V_{DDQ}/2$ | (V <sub>DDQ</sub> /2) + 0.2 | V    |

| l <sub>oz</sub>  | High-Impedance Output Current                      | $V_{O} = GND \text{ or } V_{O} = V_{DDQ}$          | -10                            |             | 10                          | μA   |

| IDDQ             | Dynamic Supply Current <sup>[8]</sup>              | All V <sub>DDQ</sub> , F <sub>O</sub> = 170 MHz    |                                | 235         | 300                         | mA   |

| I <sub>DD</sub>  | PLL Supply Current                                 | V <sub>DDA</sub> only                              |                                | 9           | 12                          | mA   |

| I <sub>DDS</sub> | Standby Supply Current                             | PD# = 0 and CLK/CLK# < 10<br>MHz                   |                                |             | 100                         | μA   |

| Cin              | Input Pin Capacitance                              |                                                    |                                |             | 4                           | рF   |

#### AC Electrical Specifications (AV<sub>DD</sub> = $V_{DDQ}$ = 2.5V±5%, T<sub>A</sub> = 0 °C to +85 °C) <sup>[9, 10]</sup>

| Parameter                              | Description                | Condition                          | Min. | Тур. | Max. | Unit |

|----------------------------------------|----------------------------|------------------------------------|------|------|------|------|

| f <sub>CLK</sub>                       | Operating Clock Frequency  | $AV_{DD}, V_{DDQ} = 2.5V \pm 0.2V$ | 60   |      | 200  | MHz  |

| t <sub>DC</sub> Input Clock Duty Cycle |                            |                                    | 40   |      | 60   | %    |

| t <sub>LOCK</sub>                      | Maximum PLL lock Time      |                                    |      |      | 100  | μs   |

| D <sub>TYC</sub>                       | Duty Cycle <sup>[11]</sup> | 60 MHz to 100 MHz                  | 49.5 | 50   | 50.5 | %    |

|                                        |                            | 101 MHz to 170 MHz                 | 49   |      | 51   | %    |

| tsl(o)                                 | Output Clocks Slew Rate    | 20%-80% of VOD                     | 1    |      | 2    | V/ns |

Notes:

2. Multiple Supplies: The Voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.

Unused inputs must be held HIGH or LOW to prevent them from floating.

Differential input signal voltage specifies the differential voltage VTR–VCPI required for switching, where VTR is the true input level and VCP is the complementary input level. See *Figure 6*.

5. Differential cross-point input voltage is expected to track V<sub>DDQ</sub> and is the voltage at which the differential signal must be crossing.

6. For load conditions see Figure 6.

7. The value of VOC is expected to be (VTR + VCP)/2. In case of each clock directly terminated by a 120Ω resistor. See Figure 6.

8. All outputs switching load with 14 pF in  $60\Omega$  environment. See Figure 6.

Parameters are guaranteed by design and characterization. Not 100% tested in production.

10. PLL is capable of meeting the specified parameters while supporting SSC synthesizers with modulation frequency between 30kHz and 50 kHz with a down spread or -0.5%.

11. While the pulse skew is almost constant over frequency, the duty cycle error increases at higher frequencies. This is due to the formula: duty cycle =  $t_{WHC}/t_c$ , where the cycle time(tC) decreases as the frequency goes up.

## CY2SSTV857-27

### AC Electrical Specifications (AV<sub>DD</sub> = V<sub>DDQ</sub> = 2.5V $\pm$ 5%, T<sub>A</sub> = 0 °C to +85 °C)(continued)<sup>[9, 10]</sup>

| Parameter                           | Description                                          | Condition      | Min. | Тур. | Max. | Unit |

|-------------------------------------|------------------------------------------------------|----------------|------|------|------|------|

| t <sub>PZL</sub> , t <sub>PZH</sub> | Output Enable Time <sup>[12]</sup><br>(all outputs)  |                |      | 3    | 25   | ns   |

| t <sub>PLZ</sub> , t <sub>PHZ</sub> | Output Disable Time <sup>[12]</sup><br>(all outputs) |                |      | 3    | 8    | ns   |

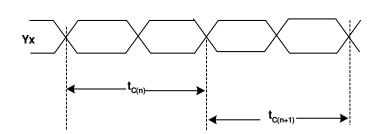

| t <sub>CCJ</sub>                    | Cycle to Cycle Jitter [10]                           | f > 66 MHz     | -75  | -    | 75   | ps   |

| tjit(h-per)                         | Half-period jitter <sup>[10, 13]</sup>               | f > 66 MHz     | -100 | _    | 100  | ps   |

| t <sub>PLH</sub> (t <sub>PD)</sub>  | Low-to-High Propagation Delay, CLK to Y              | Test Mode only | 1.5  | 3.5  | 7.5  | ns   |

| t <sub>PHL</sub> (t <sub>PD)</sub>  | High-to-Low Propagation Delay, CLK to Y              |                | 1.5  | 3.5  | 7.5  | ns   |

| t <sub>SK(O)</sub>                  | Any Output to Any Output Skew <sup>[14]</sup>        |                |      |      | 100  | ps   |

| t <sub>PHASE</sub>                  | Phase Error <sup>[14]</sup>                          |                | -50  |      | 50   | ps   |

Notes:

Refers to transition of non-inverting output.

Period jitter and half-period jitter specifications are separate specifications that must be met independently of each other.

All differential input and output terminals are terminated with 120Ω/16 pF, as shown in *Figure 5*.

## CY2SSTV857-27

### Ordering Information

| Part Number       | Package Type               | Product Flow              |

|-------------------|----------------------------|---------------------------|

| CY2SSTV857ZC-27   | 48-pin TSSOP               | Commercial, 0° to 70°C    |

| CY2SSTV857ZC-27T  | 48-pin TSSOP–Tape and Reel | Commercial, 0° to 70°C    |

| CY2SSTV857ZI-27   | 48-pin TSSOP               | Industrial, -40° to +85°C |

| CY2SSTV857ZI-27T  | 48-pin TSSOP–Tape and Reel | Industrial, -40° to +85°C |

| Lead-Free         |                            | i                         |

| CY2SSTV857ZXC-27  | 48-pin TSSOP               | Commercial, 0° to 70°C    |

| CY2SSTV857ZXC-27T | 48-pin TSSOP–Tape and Reel | Commercial, 0° to 70°C    |

| CY2SSTV857ZXI-27  | 48-pin TSSOP               | Industrial, -40° to +85°C |

| CY2SSTV857ZXI-27T | 48-pin TSSOP–Tape and Reel | Industrial, -40° to +85°C |

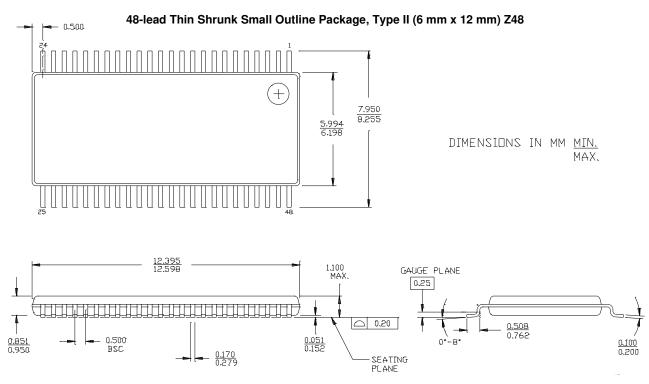

### Package Drawing and Dimension

While SLI has reviewed all information herein for accuracy and reliability, Spectra Linear Inc. assumes no responsibility for the use of any circuitry or for the infringement of any patents or other rights of third parties which would result from each use. This product is intended for use in normal commercial applications and is not warranted nor is it intended for use in life support, critical medical instruments, or any other application requiring extended temperature range, high reliability, or any other extraordinary environmental requirements unless pursuant to additional processing by Spectra Linear Inc., and expressed written agreement by Spectra Linear Inc. Spectra Linear Inc. reserves the right to change any circuitry or specification without notice.